Willkommen beim Projekt THANNA

Neuronale Netze revolutionieren die Welt der Bilderkennung, der Generierung

von Bildern und der Sprachinterpretation. Doch mit ihrer zunehmenden

Komplexität steigt auch der Bedarf an Rechenleistung für schnelle

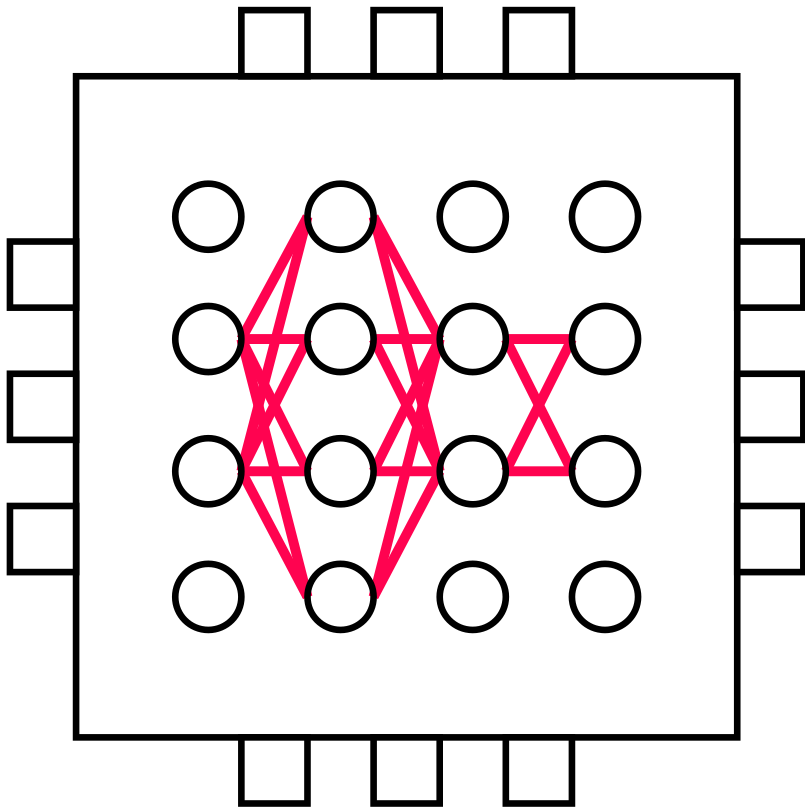

Inferenzzeiten. Programmierbare Logik in Form von FPGAs sind für diesen

Anwendungsfall als Plattform besonders gut geeignet: deren Programmierbarkeit

erlaubt es, die Hardware an die Algorithmen bestmöglich anzupassen

und so auch Neuronale Netze so effizient wie möglich zu beschleunigen.

Das Projekt THANNA (TH-Augsburg-Neural-Network-Accelerator)

hat sich zum Ziel gesetzt ein neues, offenes Framework zu entwickeln,

das die Inferenz Neuronaler Netze mit Hilfe von programmierbarer Logik (FPGAs) beschleunigt.

THANNA besteht aus ...

- ... einer Software, die zur Optimierung von Neuronalen Netzen dient (Sprache: Python)

- ... einem Embedded-Linux-Treiber, der mit dem Hardware-Beschleuniger kommuniziert (Sprachen: C, Python)

- ... einer effizienten und flexiblen Beschleuniger-Hardware, die in programmierbarer Logik implementiert ist (Sprachen: TCL, VHDL)

Das Projekt startete Mitte 2023, aktuell sind mehrere begeisterte

Studierende involviert, die hier im Rahmen von Projekt- oder

Abschlussarbeiten mitwirken.

Weitere Informationen

Studierende Aufgepasst!

Möchten Sie Teil dieses spannenden Projekts werden? Oder interessieren

Sie sich für andere Beteiligung am Projekt? Wir laden Sie ein, sich uns

anzuschließen und die Zukunft des THANNA-Projekts mitzugestalten –

zum Beispiel im Rahmen Ihrer Abschlussarbeit, von Projektarbeiten oder

Wahlpflichtfächern.